Bruce Jacob

University of Maryland

SLIDE I

Bruce Jacob University of Maryland

**PERSPECTIVE:**

| ARYLAS |

|--------|

|--------|

|               | Cost for | Power for | Power    |

|---------------|----------|-----------|----------|

|               | I0 GB    | I0 GB     | per GB/s |

| Off-Chip SRAM | \$1,000  | 0.4 W     | 0.2 W    |

| DDR3 SDRAM    | \$100    |           | 0.2 W    |

| NAND Flash    | \$10     | 0 W       | 3 W      |

|               |          |           |          |

Bruce Jacob

University of Maryland

SLIDE 2

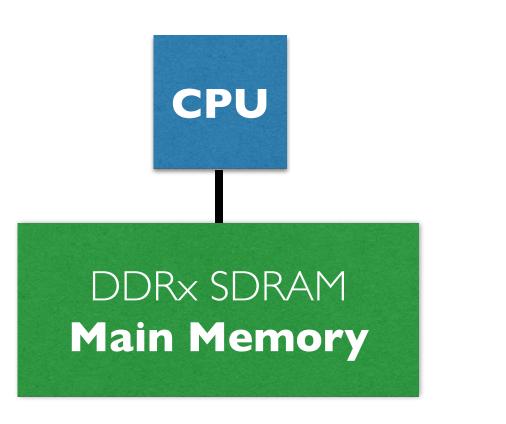

## Flash-Based Main Memory

Note: wear-out is mitigated by using MANY devices (thousands). A single device would wear out in under two days; therefore, 1000 devices should last for at least a year.

Bruce Jacob

University of Maryland

SLIDE 3

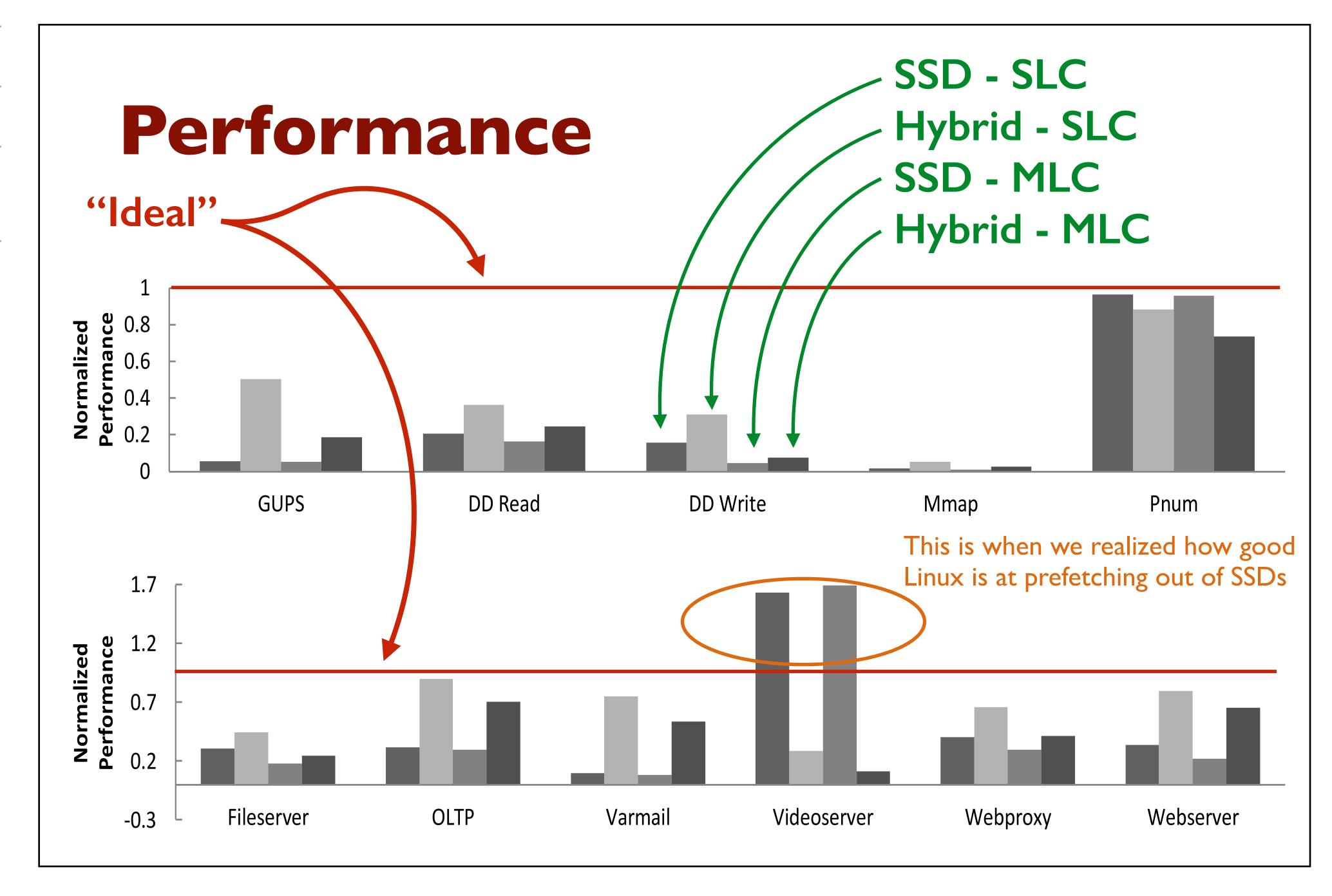

## Flash-Based Main Memory

Bruce Jacob

University of Maryland

SLIDE 4

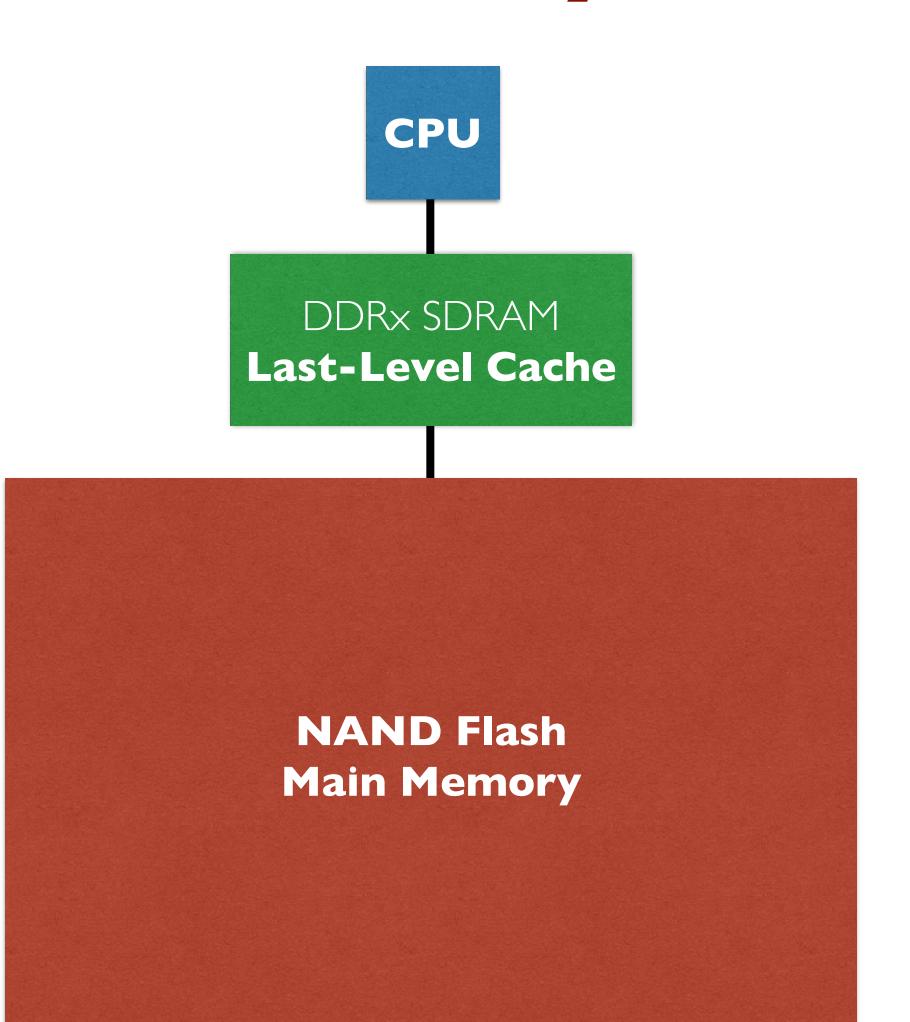

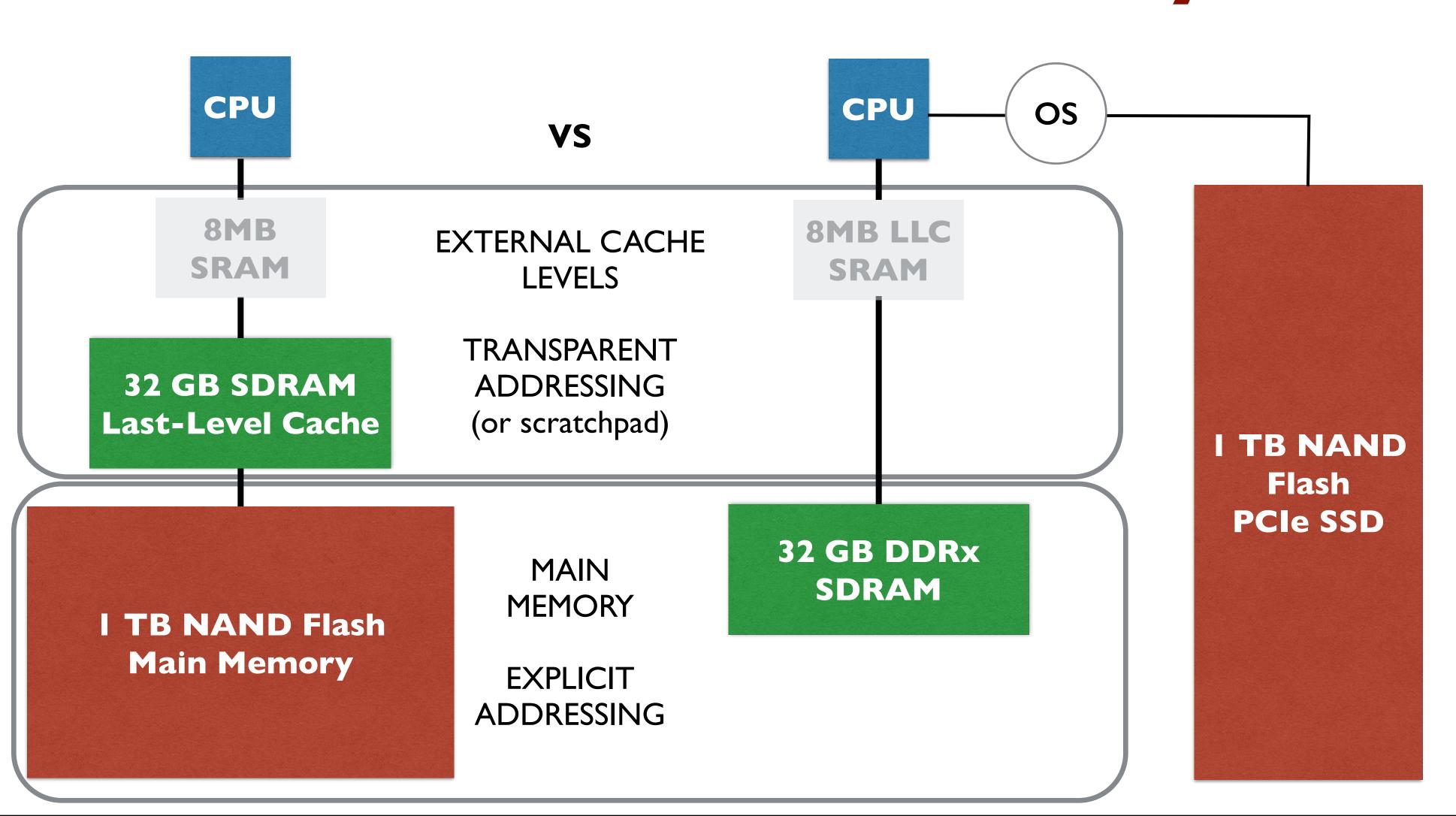

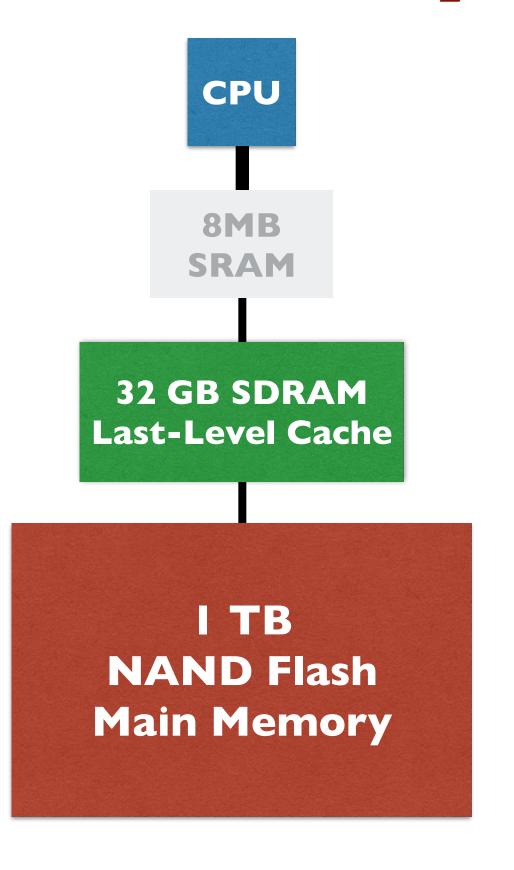

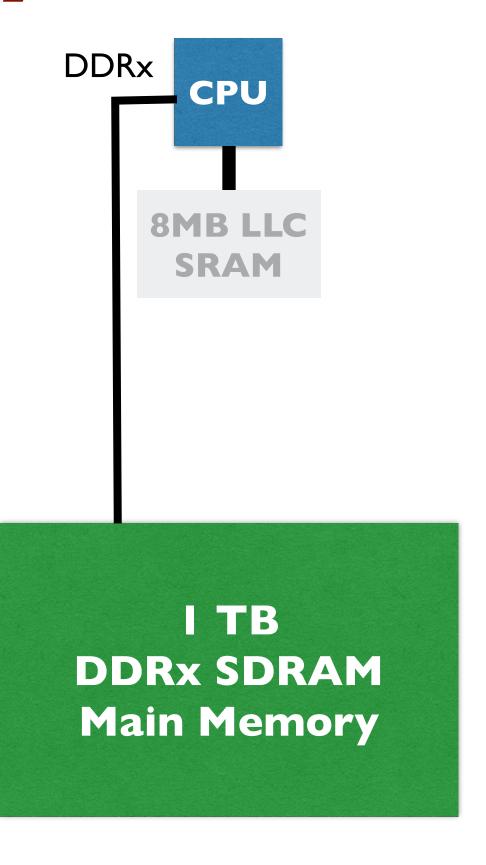

# A Tale of 3 Memory Systems

I TB

NAND Flash

PCIe SSD (I/O)

**SSD** \$500 – 10W

Hybrid \$500 - 10s of W

Ideal \$10,000 – 100W

Bruce Jacob

University of Maryland

SLIDE 5

Bruce Jacob

University of Maryland

SLIDE 6

## Less Easily Quantified Stuff

#### Out of the box:

- Journaled main memory built-in checkpoint/repair (flash side-effect)

- No VM or TLB needed (flash maps self)

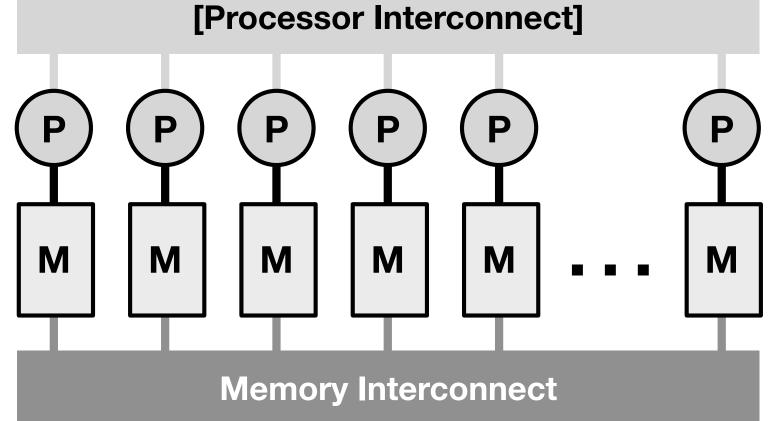

If HMC-type intra-memory network used:

- · Global physical space

- · ... even virtual

Bruce Jacob

University of Maryland

SLIDE 7

#### Bottom Line

Your future is non-volatile ... and BIG

- Less expensive

- Lower power

- Performance approaching that of DRAM

Global address space for free

Checkpoint/repair built-in

What we need from you: BIG benchmarks