### YOUR NEW STANDARD FOR MEMORY PERFORMANCE

### **Todd Farrell**

Senior Member Technical Staff Computing and Networking BU

tfarrell@micron.com

©2014 Micron Technology, Inc.

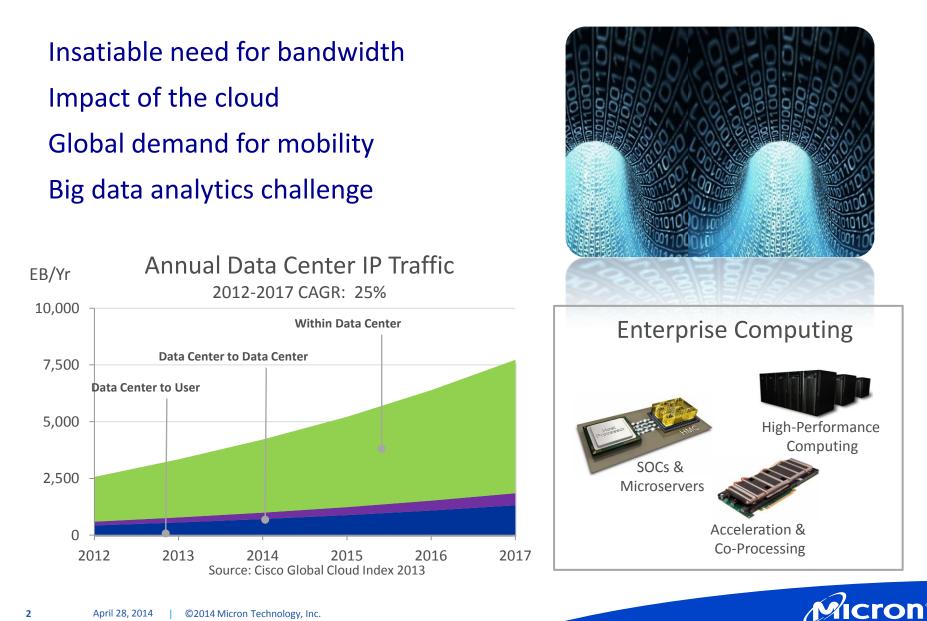

### **Demand Drivers**

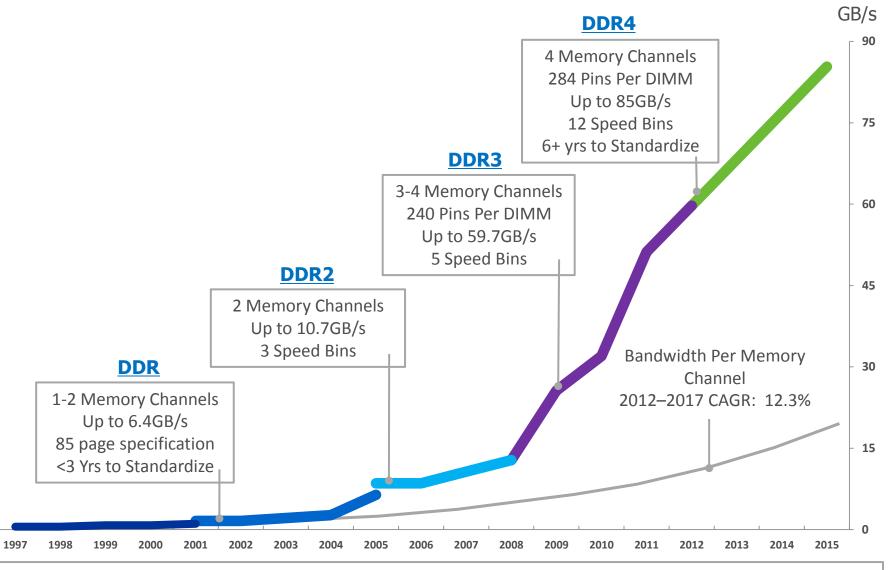

### Historical System Bandwidth, Cost, and Complexity

#### **Traditional Memory Designs Do Not Scale and Drive Exponential Complexity**

*licron*

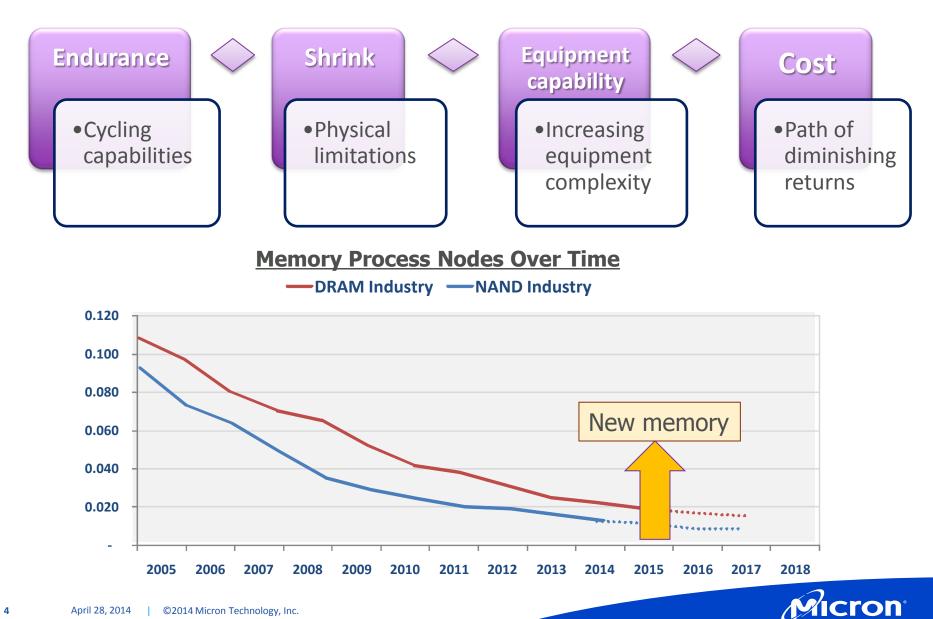

### Major Challenges to the Longevity of DRAM and NAND Technologies

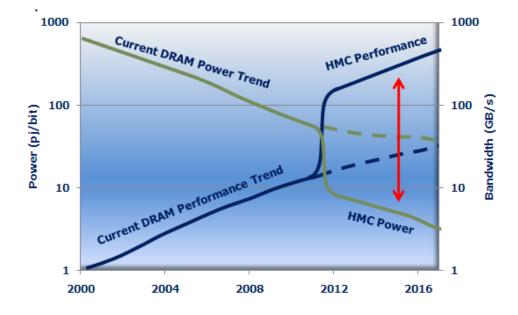

### HMC - A Revolutionary Shift

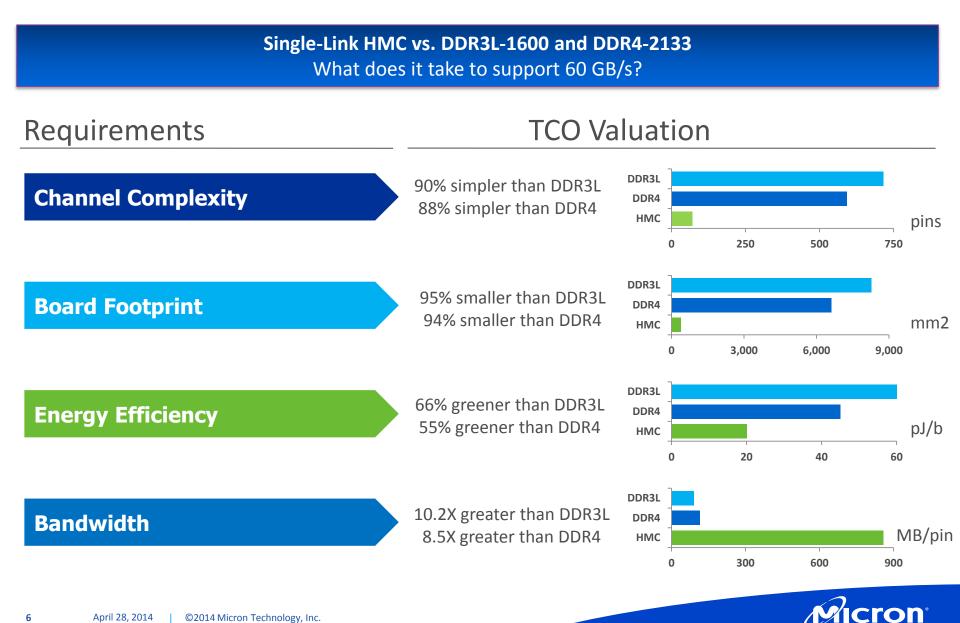

### **High-Performance Memory Comparison**

## **Enabling Technologies**

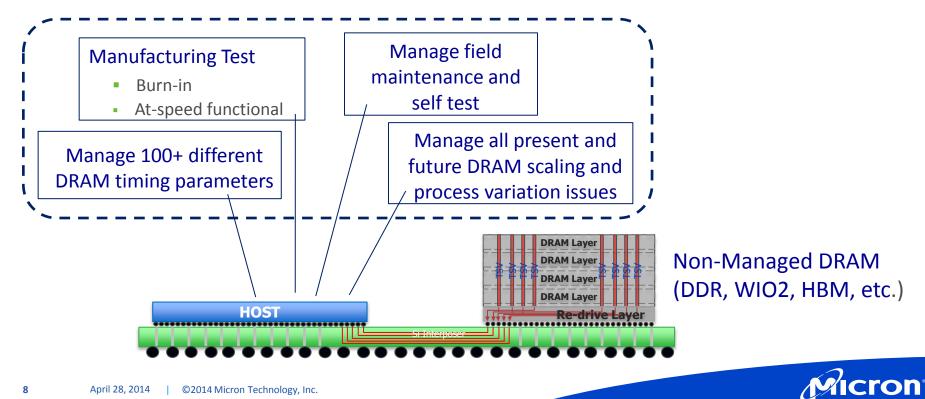

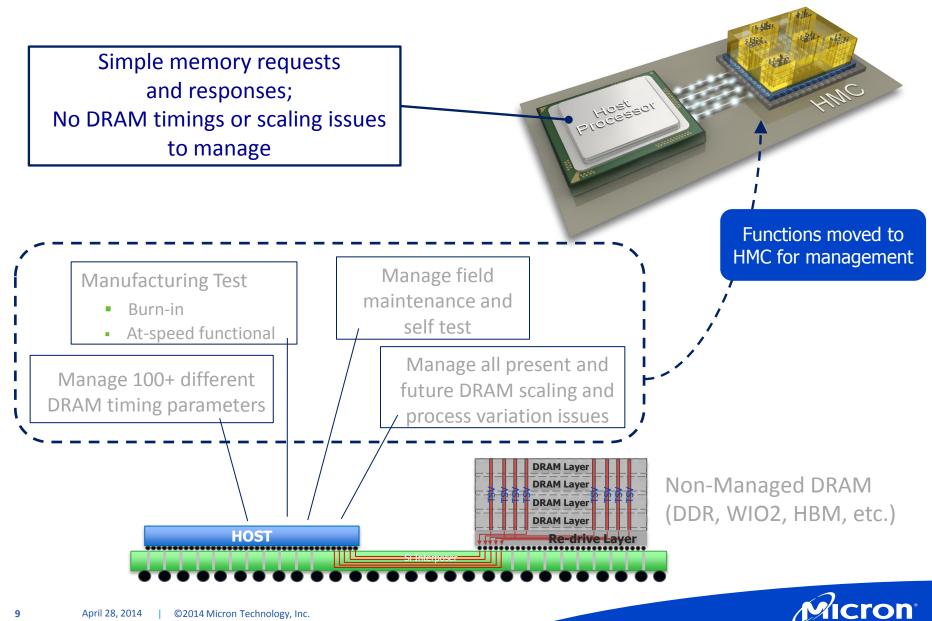

#### **Abstracted Memory Management**

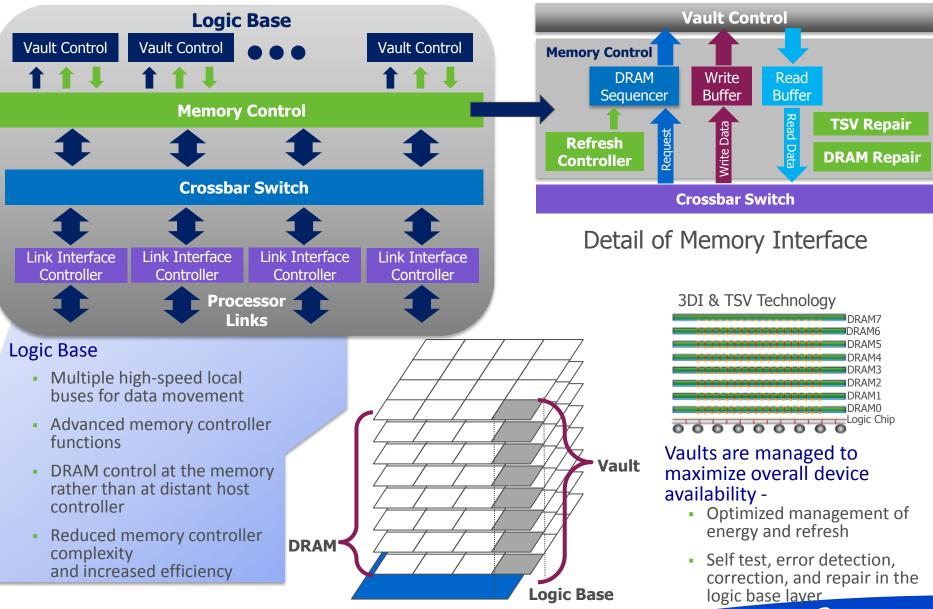

#### Memory Vaults vs. DRAM Arrays

Significantly improves bandwidth, quality, and reliability vs. traditional DRAM technologies

#### Logic Base Controller

- Reduces memory complexity and significantly increases performance

- Allows memory to scale with CPU performance

#### Through-Silicon Via (TSV) Assembly

#### **Innovative Design & Process Flow**

- Incorporates thousands of TSV sites per die to reduce signal lengths and power

- Enables memory scalability through parallelism

#### Sophisticated Package Assembly

Provides higher component density and significantly improves signal integrity

### **Traditional Host Processor Memory Management**

### Simple HMC Memory Management

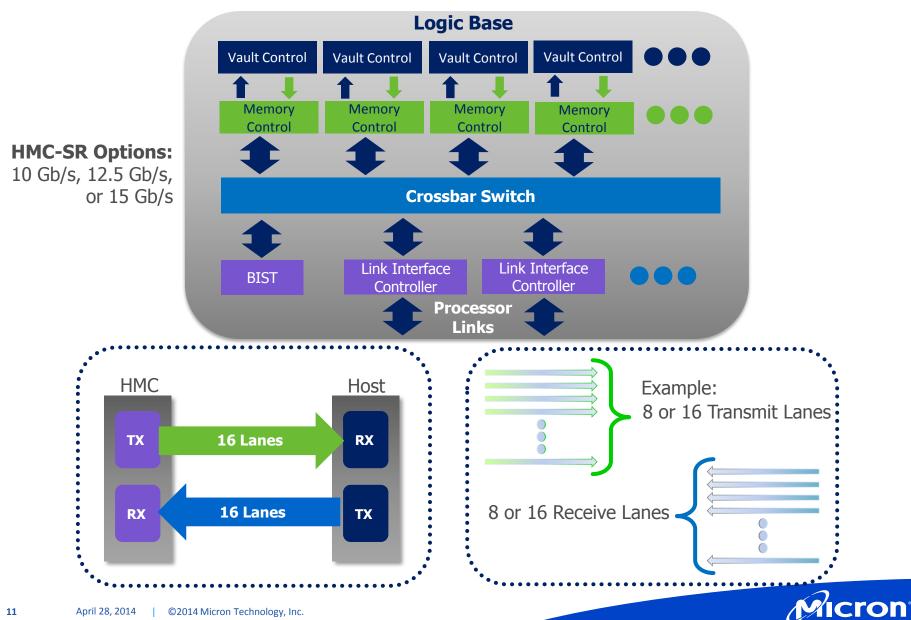

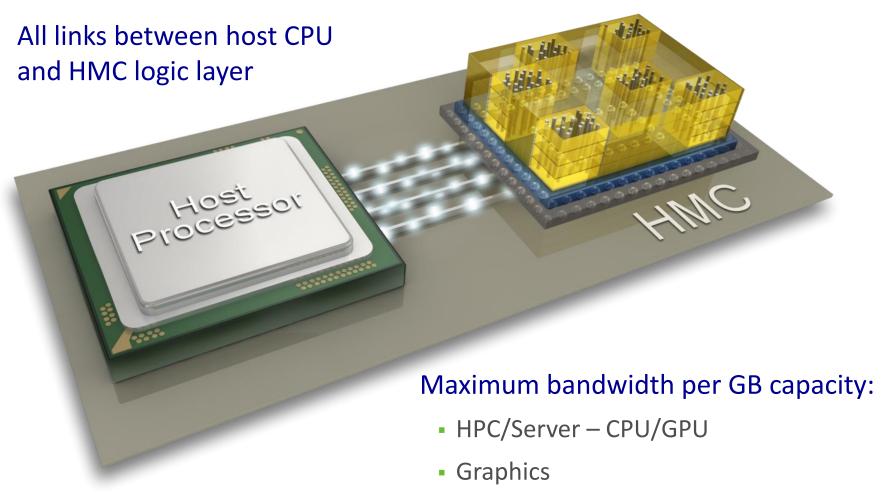

### **HMC** Architecture

### **HMC** Architecture Link Controller Interface

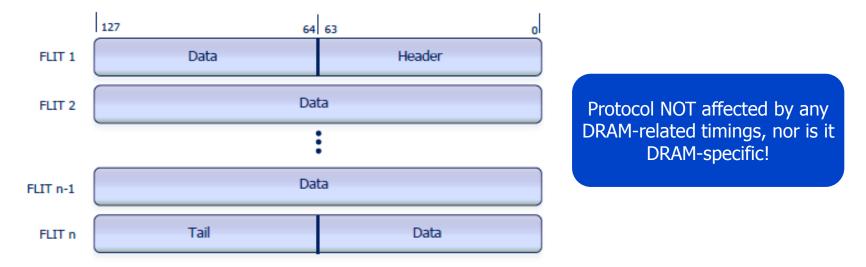

### **Packet-Based Communication**

### Packets comprised of 128-bit (16-byte) FLITs

Packets include 1 to 9 FLITs, depending on command

Host issues requests & HMC issues responses

# Each packet contains 64-bit header and 64-bit tail (1 FLIT)

Multiple data transfer sizes supported (16B to 128B)

Commands include reads, writes, atomics, error responses

Simultaneous READs and WRITEs supported

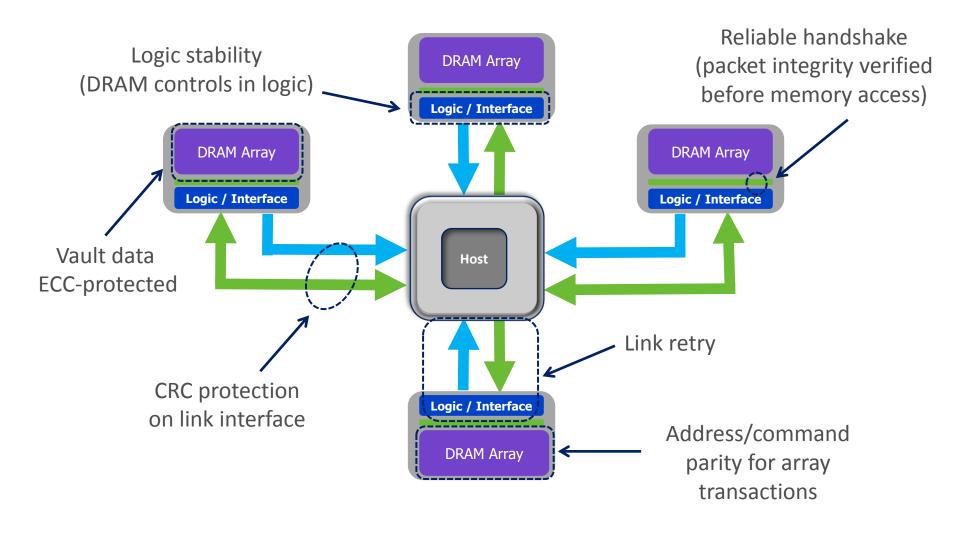

### HMC Reliability Built-in RAS features

### **RAS Feature System Comparison**

| FEATURE                               | DRAM | RDIMM | НМС          |

|---------------------------------------|------|-------|--------------|

| Extensive Test Flow                   | ✓    |       | ✓            |

| Data ECC                              |      | ✓     | ✓            |

| Address/Command Parity                |      | ✓     | ✓            |

| Mirroring<br>(back-up memory)         |      |       | <b>~ ~</b>   |

| Sparing (Chipkill)                    |      |       | <b>√</b> √   |

| Lockstep<br>(redundancy w/better ECC) |      |       | ~ ~          |

| CRC Coding                            |      |       | ✓            |

| Self Repair                           |      |       | ✓            |

| BIST                                  |      |       | ✓            |

| Error Status<br>and Debug Registers   |      |       | √            |

| DIMM Isolation<br>(flags faulty DIMM) |      |       | 44           |

| Memory Scrubbing                      |      |       | $\checkmark$ |

✓ Supported ✓ ✓ Redundant or not needed

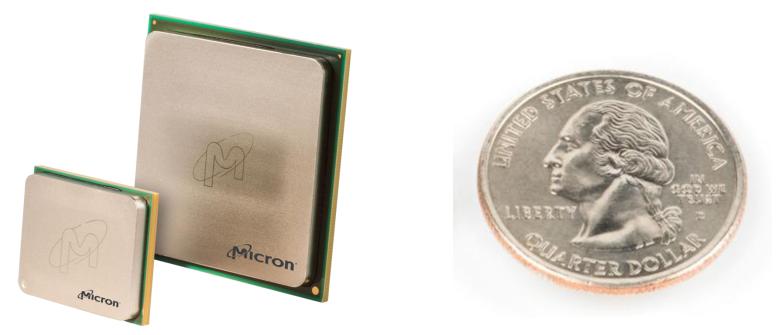

### **HMC Standard Packages**

Up to 1.28 Tb/s memory bandwidth available TODAY!

Standard BGA packaging solutions: Cost-effective packaging using existing ecosystems MCM and In-Package options available

### HMC Maximum Bandwidth Configurations

- Networking systems

- Test equipment

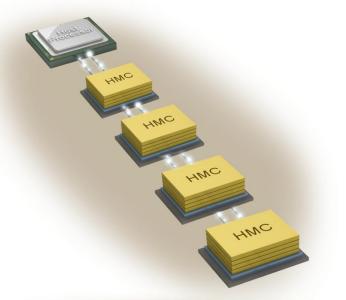

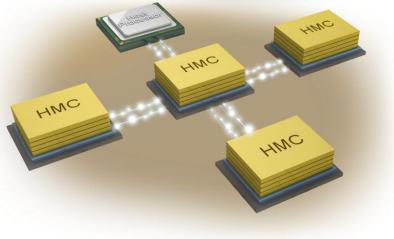

### **HMC Scalable Memory Solutions**

#### Far Memory:

- Some HMC links connect to host some to other cubes

- Scalable to meet system requirements

- Available in module form or soldered-down

- Building blocks for multiple application needs

### Future Products May Include:

- Higher-speed electrical (SERDES) VSR-30

- Optical interfaces (align to industry stds.)

- Higher stack count for greater capacity

- Non-DRAM memory technologies

- Additional Atomic Operations inside Cube

## Hybrid Memory Cube

#### **Micron Memory Innovation**

We've combined fast logic process technology and advanced DRAM designs to create an entirely new category of memory. Hybrid Memory Cube (HMC) technology provides a high-bandwidth, low-energy, high-density memory system that's unlike anything on the market today.

#### **Unprecedented Performance**

HMC will provide a revolutionary performance shift that will enrich next-generation networking and enable exaflop-scale supercomputing:

> **Reduced Power** Fraction of the energy per bit

**Reduced Footprint** 90% less space than today's RDIMMs

#### **Increased Bandwidth** 15X the performance of DDR3\*

\* HMC SR-15G vs. DDR3-1333

### **Industry Validation**

"...unprecedented levels of memory performance" - Electronic News

"...like adding a turbocharger to your computer" - datacenteracceleration.com

"...get ready for some serious bandwidth to hit us in the near future"

- tweaktown.com

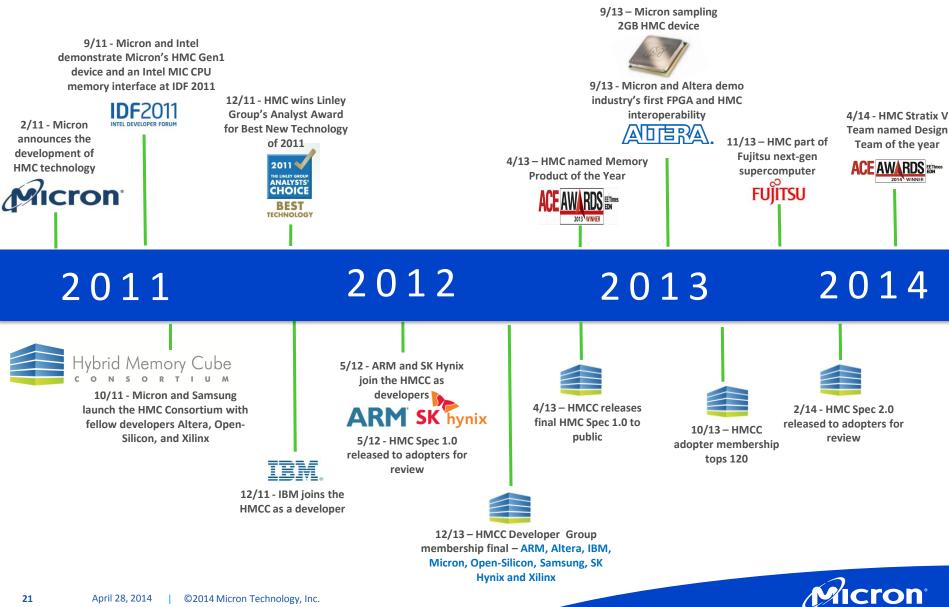

### **Consortium Momentum**

http://www.hybridmemorycube.org

### **Milestones**

### HMC - A Revolutionary Shift

# **Thank You!**

©2014 Micron Technology, Inc. All rights reserved. Products are warranted only to meet Micron's production data sheet specifications. Information, products, and/or specifications are subject to change without notice. All information is provided on an "AS IS" basis without warranties of any kind. Dates are estimates only. Drawings are not to scale. Micron and the Micron logo are trademarks of Micron Technology, Inc. All other trademarks are the property of their respective owners.